Teemu Kangasharju

# SOFTWARE ARCHITECTURE FOR LOW TIER EMBEDDED PRODUCT PLATFORM

# SOFTWARE ARCHITECTURE FOR LOW TIER EMBEDDED PRODUCT PLATFORM

Teemu Kangasharju Master's thesis Autumn 2012 Degree program in Information Technology (Master of Engineering) Oulu University of Applied Sciences

# ABSTRACT

# OULLU UNIVERSITY OF APPLIED SCIENCES Degree programme Thesis Pages / enclosures Degree Programme in Information Technology Master's Thesis 59 / 3 Line Date 2012 Commissioned by Author Teemu Kangasharju

Thesis title

SOFTWARE ARCHITECTURE FOR LOW TIER EMBEDDED PRODUCT PLATFORM

The purpose of this thesis is to describe embedded software platform architecture for low tier applications. The point of view of this software platform description is hardware oriented. General trends influence the solutions that have been selected to the final architectural design of the software platform. The Open Source Software (OSS) is becoming more common in the software product development. Many chip manufacturers offer a comprehensive baseline for the development software and the whole embedded system. Development communities and system development companies re-develop the open software components and hardware components to final, type approved products.

Nowadays it is very common that a customer has some product or business idea which should be processed to a final product onto the market. The customer in this case means the organization who wants to purchase an R&D and/or productization project from someone else. Other starting points for this work are low tier and low cost aspects. The processor / microcontroller and Real Time Operating System (RTOS) choices are significant factors when designing a modular and cost efficient embedded system.

The main aim of the thesis is to create architectural design for an embedded product platform. It gives the preliminary solutions to develop modular, configurable, and maintainable embedded systems.

Keywords: Embedded software platform, Software architecture, Low tier product platform, RTOS, Embedded systems, Open source software, Wireless

# PREFACE

I graduated as an Engineer of Computer Science from Raahe Institute of Computer Science in 2001. The first couple of years after the graduation I worked at Buscom Oy. Buscom Oy is known as Fara Oy nowadays. My responsibilities were smart card related tasks in software development. I left Buscom Oy at the end of 2006.

I started at Sweco Industry Oy at the beginning of 2007 as software specialist. Sweco Industry is a consultant house. I started in a team that developed an automated test system for digital Application Specific Integrated Circuits (ASIC) in the cellular phone platform development. The work tasks were embedded software mainly. In April 2010 Lewel Group Finland Oy bought the electronic and mechanic departments from Sweco Industry and the employees continued as old workers.

In the autumn of 2010 we started to plan the Fast Prototyping Platform to boost an entire Research and Development (R&D) project selling for customers speeding up the product development. I have been the software architect in the development. Low Tier Device (LTD) platform development started in the autumn of 2011. The engineering work of the LTD Platform has been done as collaboration with Oulu and Kuopio people. This thesis describes the work of the LTD platform software architecture.

I would like to thank all Lewel people which are involved in my daily work. I thank employees which participated to the LTD platform development; Aleksi Ukkola, Mika Tapaninaho, Markus Paldanius, Kari Salo, Juha Kortesalmi, Mikko Alafrantti, Tommi Takkinen and as well as Marko Pylkkänen and Markku Soininen the professionals of Kuopio. They all ensured that the thesis reached its target. I would like to direct special thanks to Hannu Ylönen, the system architect of LTD and the mentor of this thesis in addition, I thank the thesis supervisor Kari Laitinen from OUAS.

Oulu, Finland, August 2012

Teemu Kangasharju

# CONTENTS

| 1 | INTE  | RODUCTION                                         | 9 |

|---|-------|---------------------------------------------------|---|

|   | 1.1   | Embedded Software Development                     | 9 |

|   | 1.2   | The Idea of Embedded Software Product Platform    | Э |

|   | 1.3   | Outline of the Thesis10                           | ) |

| 2 | EME   | BEDDED SOFTWARE PLATFORM12                        | 2 |

|   | 2.1   | Product Development12                             | 2 |

|   | 2.2   | Technical Trends12                                | 2 |

|   | 2.3   | Wireless Subsystems13                             | 3 |

| 3 | RES   | EARCH PROBLEM15                                   | 5 |

|   | 3.1   | Problem Definition15                              | 5 |

|   | 3.1.1 | Business Oriented Approach15                      | 5 |

|   | 3.1.2 | Product Development Oriented Approach16           | 5 |

|   | 3.2   | Technical Requirements for LTD Product Platform17 | 7 |

|   | 3.2.1 | Software Requirements17                           | 7 |

| 4 | LTD   | SW ARCHITECTURE                                   | Э |

|   | 4.1   | Introduction19                                    | Э |

|   | 4.1.1 | LTD API Services22                                | 2 |

|   | 4.1.2 | Operating System – MQX23                          | 3 |

|   | 4.1.3 | LTD Hardware Abstraction Layer                    | 1 |

|   | 4.1.4 | LTD BSP Configuration25                           | 5 |

|   | 4.2   | LTD Software Architecture Description25           | 5 |

|   | 4.2.1 | Interface Description                             | 7 |

|   | 4.3   | Software Component Description                    | Э |

|   | 4.3.1 | Application Level                                 | Э |

|   | 4.3.2 | Low Tier Device API Layer                         | ) |

|   | 4.3.3 | LTD Hardware Abstraction Layer                    | 1 |

|   | 4.3.4 | LTD BSP Creation                                  | 2 |

| 5 CON   | NCLUSION                              | 54 |

|---------|---------------------------------------|----|

| 5.1     | Results                               | 54 |

| 5.1.1   | CPU Subsystem                         | 54 |

| 5.1.2   | Low Tier Device Board Support Package | 54 |

| 5.1.3   | Communication                         | 55 |

| 5.1.4   | User Interface                        | 55 |

| 5.2     | Further Development Possibilities     | 55 |

| 5.2.1   | USB On The Go                         | 56 |

| 5.2.2   | Power Management                      | 56 |

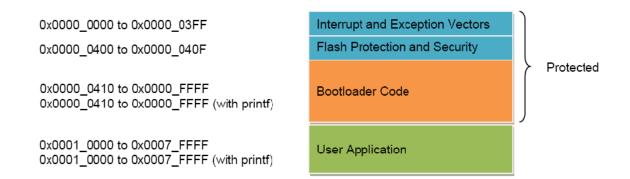

| 5.2.3   | Bootloader                            | 57 |

| 5.2.4   | Bluetooth Low Energy                  | 57 |

| REFEREN | NCES                                  |    |

# **TERMS AND ABBREVIATIONS**

| LTD  | Low Tier Device                         |

|------|-----------------------------------------|

| API  | Application Programming Interface       |

| LCD  | Liquid Crystal Display                  |

| ASIC | Application Specific Integrated Circuit |

| HAL  | Hardware Abstraction Layer              |

| BSP  | Board Support Package                   |

| RTOS | Real Time Operating System              |

| MQX  | Freescale RTOS                          |

| FFS  | Flash File System                       |

| MFS  | MQX File System                         |

| OTG  | On The Go                               |

| РМ   | Power Management                        |

| HMI  | Human Machine Interface                 |

| SoC  | System on Chip                          |

| SDK  | Software Development Kit                |

| ADC  | Analog to Digital Converter             |

| DAC  | Digital to Analog Converter             |

| BT   | Bluetooth                               |

| BLE  | Bluetooth Low Energy                    |

| РХР  | BLE Proximity Profile       |

|------|-----------------------------|

| GAP  | Generic Access Profile      |

| GATT | Generic Attribute Profile   |

| WLAN | Wireless Local Area Network |

- OSS Open Source Software

- I2C multi-master serial single-ended computer bus

- SPI Serial Peripheral Interface

- SDIO Secure Digital Input Output

- GPL General Public License

- LSB Least Significant Bit

- VLPS Very Low Power Stop mode

- VLPR Very Low Power Run mode

- PGA Pin Grid Array

- FAT File Allocation Table

- GUI Graphical User Interface

- RTC Real Time Clock

- PLL Phase Lock Loop

- FLL Frequency Lock Loop

- MCG Multipurpose Clock Generation

- FBE FLL Bypassed External

## **1 INTRODUCTION**

This chapter introduces the focus of the thesis. It describes special features of an embedded software development. In addition, the idea of the embedded software platform is presented shortly in this chapter.

#### **1.1 Embedded Software Development**

When planning software for embedded systems, it has to be considered from a different point of view than in the general software development. Embedded software often has to deal with memory constraints, critical timing demands, power consumption demands, etc. When constructing embedded systems to some specific areas such as medical, automotive, telecommunications or consumer electronics, these rules and constraints should be applied into development. It is a common trend that embedded systems have to be small, cheap and powerful.

#### 1.2 The Idea of Embedded Software Product Platform

Nowadays it is very common that a customer has some product or business idea which should be processed to final a product onto the market. The customer in this case means the organization who can be a product owner, who wants to purchase an R&D and/or productization project from someone else. They have not necessarily the engineering resources and knowledge to get progress for it. This thesis gives some answers for these demands from the software perspective. The thesis presents one solution to create an embedded software platform.

This Software architecture design is divided into two main software parts: Application Programming Interface (API) and Hardware Abstraction Layer (HAL). These parts should be operated as independently as possible of application functionality and hardware solution. It is obvious the customer's needs influence these layers, but target is that customer specific needs can be just an API service like some specific measurement technique controlling interface for application. Hardware-wise the product platform can be like a reference design, and the actual research and development work tailors it to customer specific format.

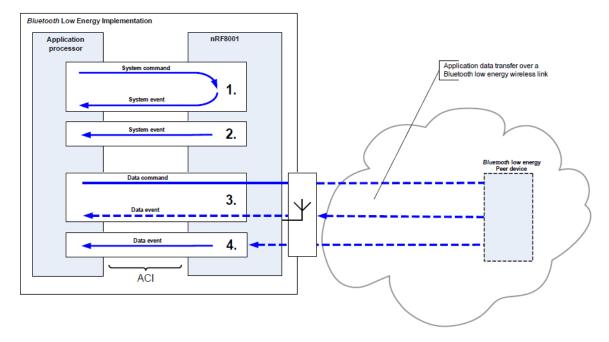

The main focus areas of the thesis work are to plan modularity and maintainable software architecture and to observe and investigate the portability of different wireless protocol stacks. Bluetooth (BT), Bluetooth Low Energy (BLE) and Wireless Local Area Network (WLAN) are the wireless technologies under review. The modularity aspect contains how easily the customer needs can be ported into basic platform set up and how easily it can be configured to another application requirements. Wireless protocol stacks are usually licensed. BLE is quite new technology, are therefore the code portability could be a challenge.

The other starting points for this master's thesis work are low tier and low cost aspects and thus the processor / microcontroller and real time operating system (RTOS) choices are significant factors when designing the modularity and cost efficient embedded system. The design tool choices allow effective designing work. The selections of the processor architecture and preliminary RTOS choice have been done before this thesis. The design processes influence the progressing of the thesis work.

One aim is to create architectural design for an embedded product platform. It gives the preliminary solutions to develop a modular, configurable and maintainable embedded software platform. Another target of this work is to open a wireless protocol stack for portability, giving guidelines for software developing work. In addition, different business areas and their standards are challenges for product designing processes.

#### **1.3 Outline of the Thesis**

Chapter 2 describes a technological and business based background of this work. It is followed by the problem research. Chapter 3 presents the requirements for this software

platform, and chapter 4 discusses the actual work. In that chapter the architecture of the software platform and its different software components are described. Chapter 5 contains a discussion about further development possibilities.

## 2 EMBEDDED SOFTWARE PLATFORM

This chapter describes a technological framework to develop an embedded system. It also presents the technical trends, which are common in the embedded product development nowadays.

#### 2.1 Product Development

Naturally, development of an entire embedded system takes time. A product development of a certain business area or technology branch (as medical, automotive, telecommunications or consumer electronics) has a big impact onto the work amounts of the system development. That is because of the standard requirements of specific technology branches. The requirement of the product life cycle management (PLM) differs widely depending on the business branch. Usually, the intent is that the product has to be launched onto the market as soon as possible.

#### 2.2 Technical Trends

The open source software (OSS) is becoming more common in the software product development. Many chip manufacturers offer a comprehensive baseline for the development software and the whole embedded system development. One business philosophy of them is to boost their electronic component selling. They open their reference designs to all, and the development communities and system development companies redevelop the open software components and hardware components ahead to the final, type approved product. Some good examples of that kind of companies are STMicroelectronics, Texas Instrument (TI) and Freescale Semiconductors. Both sides, the re-developers and component manufactures, can have benefits:

• The chip manufacturers boost their business. As usual, when more and more manufacturers sell their components, components are becoming cheaper.

- The systems development ahead, and in that way the new innovations come up more easily.

- The systems can become more reliable when it is controlled by communities.

Along the new technology development the companies make more collaboration. For example, some parts of the development or evaluation boards are compatible between different manufacturers.

The embedded systems are becoming more powerful and smaller, what is obvious, but on other hand the battery technology development does not progress so rapidly. In many cases the battery size is bigger than the other device assembly. Wireless subsystems are coming into the embedded devices. It sets challenges for minimizing the power consumption of the hand held and battery operated embedded devices.

#### 2.3 Wireless Subsystems

Electronic systems are increasingly becoming wireless. Viewing the battery operated devices in general, the wireless subsystems take a significant part of the entire power consumption of the embedded device. It is an obvious direction of the wireless technology progress. Bluetooth (BT) has evolved to Bluetooth Low energy (BLE).

Another prevailing research direction is to get a higher data transferring rate. BT based systems can be adapted to the entire system via a serial link as the Serial Peripheral Interface (SPI) bus. WLAN has two kinds of physical connection ways such as SPI and Secure Digital Input Output (SDIO). Basically, the SPI connection limits the speed of the data transferring.

Usually, the BT software stacks are licensed strictly. Therefore the stacks are not free although the BT hardware reference designs are available. The solution from the OSS side

can be found for base porting it into the embedded system. Progressing that way it is very important to know the open source licensing policy. The most common license type there is the General Public License (GPL) in the OSS world.

## **3 RESEARCH PROBLEM**

This chapter describes the approach to a principled problem of the product development. In addition, the requirements of the LTD product platform software are shown in this chapter.

#### **3.1 Problem Definition**

The problem is surveyed from two directions, the business oriented approach and the product development oriented approach.

#### 3.1.1 Business Oriented Approach

Basically, a customer has some product or business idea which should be processed to the final product onto the market as fast as possible. Briefly, the more ready a product platform is for the customer requirements, the faster the product will be on the market. Many product creation houses are developing their own platforms, and therefore competition is quite tight in this business area, which means that company has to focus on the special knowledge of them. For example, the specialty can be knowledge of some physical phenomenon or specific business sector knowhow. In this case the focus is to do an embedded product platform for low tier applications which do not have for example wireless data transfer features.

The following are competing platforms which are on the market already:

- Navicron Oy FUSIONSOFTWARE (1).

- Aava Mobile Oy Aava Core (2).

- ERNI WHITEspeed (3).

#### **3.1.2 Product Development Oriented Approach**

From a technical point of view the platform development needs comprehensive knowledge about the embedded system architectures and their subsystems. An effective and wide partner network is an important part of the system and platform development. Usually, big component manufactures do not collaborate and therefore it is important to create connections to the suppliers who can handle a component distribution effectively. A direct connection with component manufacturers means either big volumes of the end product or co-operation with well-known company.

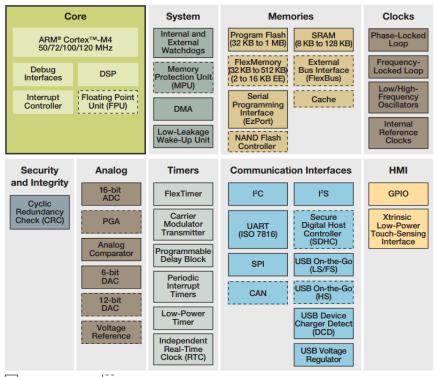

This software platform work is based on the System on Chip (SoC) of Freescale. Freescale Semiconductors is a big worldwide company. Their business philosophy is a somewhat different from that of their competitors. They open their system giving source codes of their own platform modules and they support all kinds of companies, smaller, bigger and start ups. In that way they boost their component selling. For this kind of a low tier product platform Freescale has, for example, its own open real time operating system (RTOS) named MQX. The kernel of MQX is open, Board Support Package (BSP) level code is open, and that means, a system creator has a base for starting then own platform or product development.

In an ideal situation reprocessing the end product for the customer means that existing hardware and software components are integrated in a customer specific product development project.

An expanded component library and good knowledge of the platform environment offer faster feedback for customer requirements. The following section specifies the requirement for a platform.

#### **3.2 Technical Requirements for LTD Product Platform**

The most important features to be planned were that the platform should be purposed to small, portable devices. The platform for the end product should be power consumption, size and cost efficient. The application of the device has not necessarily a support of the display component. The indication of application state can be solved by the LED blink sequence, for example.

The LTD hardware platform must be equipped with the following functional sub modules:

- CPU based on Cortex-M4 architecture. Freescale Kinetis K20

- USB 2.0 interface (LS/FS)

- On The Go (OTG) support

- PM (Power management)

- Liquid Crystal Display (LCD) I/F via GPIO

- Three LEDs & buttons

- Optional Bluetooth, BT 4.0. BLE

- I/O connector for external I/O components and peripheral devices

#### 3.2.1 Software Requirements

At the general level, the most important software requirements for LTD are related to the power consumption and code size efficiency. The operation modes of SoC should be used widely to get better efficiency. The RTOS capacity has to utilize as well as possible concerning the tight real time requirements. The software architecture should be modular the way that the new customized software components can be fitted easily to the existing system. In addition, the maintainability should be taken into account. The requirements for the LTD product platform software are:

- Freescale MQX Real Time Operating System support

- Kernel (PSP) and BSP base porting for LTD hardware

- I/O drivers for equipped hardware components of LTD

- GPIOs, I2C, SPI, Flextimer, Analog to Digital Converters (ADC), Digital to Analog Converters (DAC) etc.

- USB 2.0 interface (LS/FS) support

- On the Go (OTG) support

- OTG communication between LTD device and mobile phone (e.g. Samsung Galaxy S2)

- o BLE

- Proximity (PXP) profile support for both monitoring and reporting

- LTD should be worked as monitor and reporter

- o UI

- Sharp 96\*96 graphical LCD support

- EQUI support

- Led & Button functionality

- Test Application

- Tests functions for CPU and peripherals

- Test function menu is shown in LCD

- Test function selection by buttons

- Result of tests are indicated within LCD, LEDs and beeps of buzzer

- Detailed specification for LTD test application is described in the document LTD Test SW Design. (4).

# **4 LTD SW ARCHITECTURE**

This chapter describes the results of this work. The LTD software architecture will be cleared out in more detail in section 4.2.

#### 4.1 Introduction

This section and its sub-sections work as an introduction for the actual work of the architecture design. The point of view of this software platform description is hardware oriented. The planning of the LTD Software Architecture needs a great deal of investigations and studies of the Freescale product family. The Kinetis chip series is quite a new product family. It is based on the ARM Cortex M4 core microcontroller. Freescale has its own TWR (Tower) development platform to evaluate the Kinetis microcontrollers and peripheral devices.

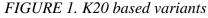

The first steps to create the entire LDT platform have been done in the TWR evaluation environment. The SoC Choice for LTD was Kinetis K20. Different Kinetis SoCs have the same core. Only some IC blocks are activated in different Kinetis configurations as can be seen in figure 1. Every Kinetis family K20 has many package and memory based variants.

#### **One-Stop Enablement** Offering-MCU + IDE + RTOS

Freescale Tower System hardware development environment:

Integrated development environments Eclipse-based CodeWarrior V10.x IDE

- and Processor Expert • IAR Embedded Workbench

- Keil MDK

- CodeSourcery Sourcery G++ (GNU)

- Runtime software and RTOS

- Math, DSP and encryption libraries

- Motor control libraries

- Complimentary bootloaders

- (USB, Ethernet, RF, serial)

- Complimentary Freescale embedded GUI

- Complimentary Freescale MQX<sup>™</sup>

- Cost-effective Nano<sup>™</sup> SSL/Nano<sup>™</sup> SSH for Freescale MQX RTOS

- Micrium uC/OS-III

- Express Logic ThreadX

- SEGGER embOS

- freeRTOS

- Mocana (security)

- Full ARM ecosystem

| Features                                                                                                                                                                                                                        | Benefits                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <ul> <li>ARM<sup>®</sup> Cortex<sup>™</sup>-M4 core with DSP<br/>instruction support and optional<br/>single precision floating point unit</li> <li>Up to 32-channel DMA. Up to 16<br/>KB of cache. Cross bar switch</li> </ul> | Up to 120 MHz core supporting a broad range of processing<br>bandwidth needs     Peripheral and memory servicing with reduced CPU loading.<br>Optimized bus bandwidth and flash execution performance.<br>Concurrent multi-master bus accesses for increased bus<br>bandwidth                                                                                              |  |  |  |  |  |  |

| USB On-The-Go (Full- and High-<br>Speed) with device charger detect                                                                                                                                                             | <ul> <li>Optimized charging current/time for portable USB devices,<br/>enabling longer battery life. USB low-voltage regulator supplies<br/>up to 120 mA off chip at 3.3V to power external components from<br/>5V input</li> </ul>                                                                                                                                        |  |  |  |  |  |  |

| Memory protection unit     Hardware cyclic redundancy check engine     Independent-clocked COP. External watchdog monitor                                                                                                       | <ul> <li>Provides memory protection for all cross bar switch masters,<br/>increasing software reliability</li> <li>Validates memory contents and communication data, increasing<br/>system reliability</li> <li>Prevents code runaway in fail-safe applications. Drives output pin<br/>to safe state external components if watchdog event occurs</li> </ul>               |  |  |  |  |  |  |

| <ul> <li>Up to four FlexTimers with up to 20 channels</li> <li>Carrier modulator transmitter</li> <li>4-channel, 32-bit periodic interrupt</li> </ul>                                                                           | General purpose timers with hardware dead-time insertion and<br>quadrature decoding for motor control     Infrared waveform generation for remote control applications     Time base generation for RTOS task scheduler or trigger source<br>for ADC conversion and programmable delay block                                                                               |  |  |  |  |  |  |

| <ul> <li>FlexBus external bus interface</li> <li>Secure digital host controller</li> <li>NAND flash controller</li> </ul>                                                                                                       | Enables the connection of external memories and peripherals<br>(e.g., graphics displays)     Connection to SD, SDIO, MMC or CE-ATA cards for in-application<br>software upgrades, file systems or adding Wi-Fi® or Bluetooth®<br>support     Supports up to 32-bit ECC current and future NAND types with<br>minimal software overhead                                     |  |  |  |  |  |  |

| <ul> <li>32 KB–1 MB flash. Up to 128 KB of<br/>SRAM</li> <li>32 KB–512 KB FlexMemory</li> </ul>                                                                                                                                 | <ul> <li>High reliability, fast access program memory with 4-level security<br/>protection. Independent flash banks allow concurrent code<br/>execution and firmware updating</li> <li>FlexMemory provides 32B–16 KB of user-segmentable byte write/<br/>erase EEPROM. In addition, FlexNVM from 32 KB–512 KB for<br/>extra program code, data or EEPROM backup</li> </ul> |  |  |  |  |  |  |

|                |           | Feature Options |               |           |            |                                         |                   |     |                                   |                       | Packages               |            |                      |                 |                 |             |             |              |                |                |                |             |                 |              |              |                 |                |

|----------------|-----------|-----------------|---------------|-----------|------------|-----------------------------------------|-------------------|-----|-----------------------------------|-----------------------|------------------------|------------|----------------------|-----------------|-----------------|-------------|-------------|--------------|----------------|----------------|----------------|-------------|-----------------|--------------|--------------|-----------------|----------------|

|                |           |                 |               |           |            | - *                                     | Unit              |     |                                   | oller                 | ace                    |            | er                   |                 |                 | FM          | FT          | LF           | MP             | LH             | LK             | MB          | ш               | ML           | мс           | LQ              | MD             |

| Part Number    | CPU (MHz) | Flash (KB)      | Flex NVM (KB) | SRAM (KB) | Cache (KB) | Single Precision<br>Floating Point Unit | Memory Protection | CAN | Secure Digital<br>Host Controller | NAND Flash Controller | External Bus Interface | 12-bit DAC | Prog. Gain Amplifier | 5V Tolerant I/O | Other           | 32QFN (5x5) | 480FN (7X7) | 48LQFP (7X7) | 64MAPBGA (5X5) | 64LQFP (10X10) | 80LQFP (12X12) | 81BGA (8X8) | 100LQFP (14X14) | 104BGA (8X8) | 121BGA (8x8) | 144LQFP (20x20) | 144BGA (13x13) |

| MK20DN32Vyy5   | 50        | 32              |               | 8         |            |                                         |                   |     |                                   |                       |                        |            | 1                    | -               | USB OTG (FS)    | 1           | 1           | 1            | 1              | 1              |                | -           | -               |              |              |                 |                |

| MK20DN64Vyy5   | 50        | 64              |               | 16        | 1          |                                         |                   |     |                                   |                       |                        |            |                      |                 | USB OTG (FS)    | 1           | 1           | 1            | 1              | 1              |                |             |                 |              |              |                 |                |

| MK20DN128Vyy5  | 50        | 128             |               | 16        |            |                                         |                   |     |                                   | ) (                   |                        |            |                      |                 | USB OTG (FS)    | 1           | 1           | 1            | 1              | 1              |                | 1           | î î             |              | 1            |                 |                |

| MK20DN512Vyy10 | 100       | 512             |               | 128       |            |                                         | 1                 | 1   | 1                                 |                       | 1                      | 1          | 1                    | 1               | USB OTG (FS)    |             |             |              |                |                | 1              | 1           | 1               |              | 1            | 1               | 1              |

| MK20FN1M0Vyy12 | 120       | 1 MB            |               | 128       | 16         | 1                                       | 1                 | 1   | 1                                 | 1                     | 1                      | 1          | 1                    | 1               | USB OTG (FS/HS) |             |             |              |                |                | -              |             |                 |              |              | 1               | 1              |

| MK20DX32Vyy5   | 50        | 32              | 32            | 8         |            |                                         |                   |     |                                   |                       |                        |            |                      |                 | USB OTG (FS)    | 1           | 1           | 1            | 1              | 1              |                |             |                 |              |              |                 |                |

| MK20DX64Vyy5   | 50        | 64              | 32            | 16        |            |                                         | -                 |     |                                   | 1                     |                        |            | 8                    | - 23            | USB OTG (FS)    | 1           | 1           | 1            | 1              | 1              |                | 8           | Q - 3           |              | 3            |                 |                |

| MK20DX128Vyy5  | 50        | 128             | 32            | 16        |            |                                         | 1                 |     |                                   | ( )<br>               |                        |            |                      |                 | USB OTG (FS)    | 1           | 1           | 1            | 1              | 1              |                |             |                 |              | 1            |                 |                |

| MK20DX64Vyy7   | 72        | 64              | 32            | 16        | Ĵ          |                                         |                   | 1   |                                   |                       | 1                      | 1          | 1                    | 1               | USB OTG (FS)    |             |             |              |                | 1              | 1              | 1           |                 |              |              |                 |                |

| MK20DX128Vyy7  | 72        | 128             | 32            | 32        |            |                                         | - i.              | 1   |                                   |                       | 1                      | 1          | 1                    | 1               | USB OTG (FS)    |             |             |              |                | 1              | 1              | 1           | 1               | 1            |              |                 |                |

| MK20DX256Vyy7  | 72        | 256             | 32            | 64        |            |                                         |                   | 1   |                                   |                       | 1                      | 1          | 1                    | 1               | USB OTG (FS)    |             |             |              |                | 1              | 1              | 1           | 1               | 1            |              |                 |                |

| MK20DX128Vyy10 | 100       | 128             | 128           | 32        |            |                                         | 1                 | 1   | 1                                 |                       | 1                      | 1          | 1                    | 1               | USB OTG (FS)    |             |             |              |                |                |                |             |                 |              |              | 1               | 1              |

| MK20DX256Vyy10 | 100       | 256             | 256           | 64        |            |                                         | 1                 | 1   | 1                                 | 8                     | 1                      | 1          | 1                    | 1               | USB OTG (FS)    | 1           |             |              |                |                | 1              | 1           | 1               |              | 1            | 1               | 1              |

| MK20FX512Vyv12 | 120       | 512             | 512           | 128       | 16         | 1                                       | 1                 | 1   | 1                                 | 1                     | 1                      | 1          | 1                    | 1               | USB OTG (FS/HS) |             |             |              | 1 A            |                |                |             |                 |              |              | 1               | 1              |

yy = package designator

The LTD product platform software is based on the Freescale Kinetis K20 SoC solution. The platform has an MQX RTOS operating system. The collection of the MQX documentation can be found in the project folder located on LTD SW\Freescale\_MQX\.

The software is created on the IAR embedded workbench development environment. The basic MQX RTOS packet does not include a Graphical User Interface (GUI) or a USB OTG stack. The Kinetis K20 Family has many variations of memory, package and feature options.

The architecture of the LTD Software consists of the following layers:

- Application layer

- API Services (RTOS, Tasks) LTD\_API + customer specific components

- Starting point of MQX version is MQX 3.70

- Hardware abstraction layer LTD\_HAL BSP

The processor component used in the design is actually a SoC on Cortex M4 CPU. The LTD uses the Freescale Kinetis K20 series processor. Figure 2 presents a top level block diagram of K20. The supported functions are dependent on the selected package. The largest 144 pin package is used in this prototype, because it allows the flexible I/O configuration. The customer application could use smaller pin counts if they are feasible.

# Kinetis K20 Family

Standard Feature

FIGURE 2. Kinetis K20 System on Chip

#### 4.1.1 LTD API Services

The purpose for this Software layer is to handle overall system resources, both hardware and software. For example, the measurement algorithms and device driver logic are built onto these level modules. API services are the interface to build a comprehensive application including RTOS resources.

LDT\_API offers the following services:

- General LTD\_API services

- MQX 3.7.0 RTOS features

- I/O configurations

- Specific HW initializations

- System recourses

- UI Services

- Buttons

- o LEDs

- Display functionality with graphics

- Communication Services

- Tasks intercommunication

- USB communication with another host device. It is handled by the USB OTG module.

- BT Low Energy protocol support. The proximity profile will be supported.

- Flash File System (FFS) handling services

- File system handling

- Application specific results can be stored in the flash memory.

- Measurement (imaginary) Services Customer specific

- Current pulse generation with Flex timer0 and DAC

- Current pulse measurement via ADC

- PM Services

- Operation mode handling

- Sleep mode handling

- Voltage monitoring and control

# 4.1.2 Operating System – MQX

The manufacturer of the used operating system describes it in the following way.

The Freescale MQX Real-Time Operating System (RTOS) provides real-time performance within a small, configurable footprint. This RTOS is designed to allow you to configure and balance code size with performance requirements. The easy-to-use API and out-of-box experience ensures first-time RTOS users can start developing their application on the day software is installed. For experienced OS developers, it is easy to migrate legacy application code to a Freescale MQX-based platform. The RTOS is tightly integrated with the latest ColdFire® processors from Freescale and provided with commonly used device drivers. The powerful Design and Development Tools are

integrated with CodeWarrior<sup>™</sup> tools to provide additional profiling and debugging capability.

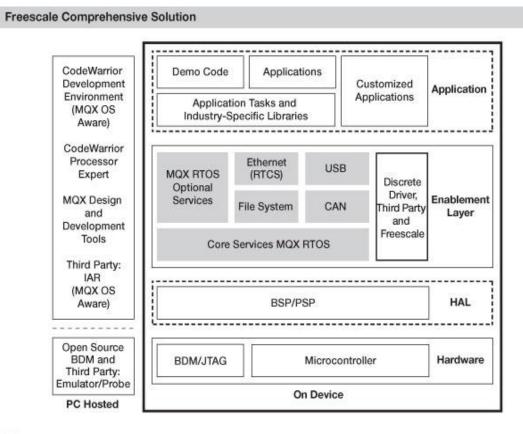

FIGURE 3. MQX RTOS – Customizable Component Set

#### 4.1.3 LTD Hardware Abstraction Layer

Hardware Abstraction Layer (HAL) abstracts physical hardware solution. The I/O drivers of hardware are located in this layer. I/O drivers of MQX are slightly deviated subset of the POSIX standard I/O. LTD product platform has own configurable BSP. Guidelines for BSP porting are presented in the document Board Support Package Porting Guide. (5).

LTD HAL offers I/O drivers for the following subsystems:

- CPU based on Cortex-M4 architecture

- USB 2.0 interface (LS/FS)

- o OTG support

- o Mass Storage device class is supported

- Power management

- User Interface

- o LCD I/F via GPIO

- Three LEDs & buttons

- Optional Bluetooth, BT 4.0

#### 4.1.4 LTD BSP Configuration

The LTD platform has its own BSP configuration including e.g. clock, processor, memory, fixed I/O lines and boot mode initializations as well as an overall control. The LDT BSP creation is based on the Board Support Package Porting Guide document. (5).

After the design and evaluation stage of developing a product with MQX has been completed, the user often wants to be migrated the application project away from a Freescale evaluation board and to a custom board. Creating a new BSP for that end board is the most advisable move. Subsection 4.4.4 contains a more detailed description the creation of LTD BSP.

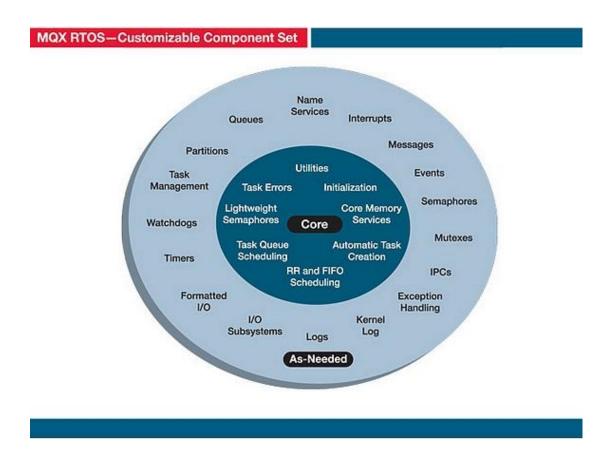

#### 4.2 LTD Software Architecture Description

Figure 4 is the core of this thesis. It describes the structure of the LTD platform software. The design of the LTD platform software follows Freescale's implementation and their paradigm using the readymade components. Three software layers are separated clearly as figure 4 presents. The architecture helps to design a modular application. Sharing layers helps to make a more maintainable system.

The LTD software architecture has been designed to be modular, reusable and maintainable as Figure 4 presents. It gives the possibility to fit different kinds of readymade and customized software components to the existing system. The purpose for the LTD API service software layer is to handle overall system resources. For example, the measurement algorithms and device driver logic are built onto these level modules. The API services are the interface to build a comprehensive application using RTOS resources. The MQX RTOS capacity is utilized for the applications which have the tight real time requirements. The software implementation has utilized the operation modes of SoC to achieve a better efficiency. The code size and code running speed optimization has been done having an advantage of the MQX configurability. The green colored blocks are the places where most of the customer specific customization is done. The FFS block means the Freescale MQX File System (MFS). It is an embedded File Allocation Table (FAT) file system compatible with The Microsoft Windows and MS-DOS file systems.

BSP - Hardware Abstraction Layer (HAL) abstracts physical hardware solution. The I/O drivers of the hardware are located on this layer. The I/O drivers of MQX are a slightly deviated subset of the POSIX standard I/O. It is recommended that a new peripheral device is taken into use via the MQX I/O control. All blocks in figure 4 are described deeply in the following sections.

FIGURE 4. LTD SW Architecture

# 4.2.1 Interface Description

The software Interfaces at the function level are presented in the following sub-sections.

There are two significant interfaces:

- HW  $\rightarrow$  HAL. The hardware is abstracted with a HAL layer

- LTD API  $\rightarrow$  APPLICATION. LTD API services applications.

## **LTD API functions**

LTD API functions are listed in Appendix 1. The Listed functions are prototypes of the functions. Inputs and outputs are documented deeply in the source code. The code module headers are as follows:

## **LTD Driver level functions**

The LTD driver level interface functions can be seen in Appendix 1. The inputs and outputs are documented deeply in the source code. The function headers are as follows:

#### 4.3 Software Component Description

#### 4.3.1 Application Level

Freescale's evaluation environment offers a many examples, applications and demo codes for the Kinetis based chips. That is one way to boost and shorten a software design cycle. The applications for the LTD board follow the software structure presented in figure 5.

Freescale MQX™ Software Solutions

FIGURE 5. Freescale MQX based solution

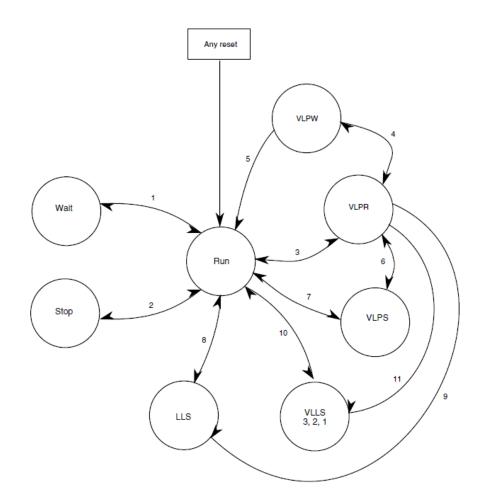

#### 4.3.2 Low Tier Device API Layer

The LTD API implements the called service level functionality as figure 6 presents. It abstracts the HW solutions and choices. That gives a possibility to use a different HW configuration and an independent application in the future. The requirements of e.g. the measurement services could be customer specific requirements. Most of the customer specific customization is done in the light green colored blocks shown in figure 6.

FIGURE 6. LTD API Level

## **General API Services**

The general API service layer offers the functionality for application. In addition to the MQX RTOS and Kinetis core features, this layer could offer higher level algorithm services by the device drivers.

General API services offer the following features:

- Kinetis core features

- Application and HW initialization

- CPU based on Cortex-M4 architecture

- MQX RTOS features

- Tasks, events, scheduler, semaphores, message handling.

- See MQX reference manual

- RTOS customization. MQX is optimized concerning the power consumption and memory wise. Small ram configuration is used.

- Core features

- Application and HW initialization

- Device I/O

- General I/O initialization.

- Clock, processor, memory, fixed I/O lines and boot mode initializations and overall control.

- LTD board related initializations to be done in BSP level. See section 4.3.3.

Most of the MQX related configurations are done in the following files:

$..\ Freescale MQX \ 3.7\mbox{wrk}\ bsp\ LTD\_BOARD\_twrk60n512\user\_config.h$

$..\Freescale MQX \ 3.7\max\source\include\max\_cnfg.h$

..\Freescale MQX 3.7\lib\LTD\_BOARD\_twrk60n512.iar\small\_ram\_config.h, Appendix 2.

The LTD BSP configuration is defined in the following header file:

..\Freescale MQX 3.7\mqx\source\bsp\LTD\_BOARD\_twrk60n512\

LTD\_BOARD\_twrk60n512.h

#### **Device Driver Services**

The device driver services are provided for the application specific functionality. Some specific algorithm is implemented at that level. That kind of services can be as follows:

- Accelerometer functionality via I2C bus

- o open, read, write implementation for 3D accelerometer

- Display functionality is performed via SPI bus

- o Individual task for graphical display is used

- I/F for application is running: *void show\_frame(char \*pixel\_data)*;

#### **Power Management Services**

The power management (PM) interface provides services for creating applications that control the power consumption. MQX supports the Kinetis specific lower power modes. The following list contains the main features of the PM services.

- Power mode handling

- Transition handling between different operation modes

- RUN, Very Low Power Stop (VLPS) and Very Low Power Run (VLPR) modes are supported

- Boot mode initializations

- Voltage control

- Battery level monitoring via ADC

#### **User Interface Services**

The UI services for creating the application offer the following features:

- Human Machine Interface (HMI) driver handling to be handled via a GPIO driver. Buttons, LEDs etc.

- Display functionality via SPI driver with some dedicated pins

- o Mono color Graphical display support

- eGUI API interface. eGui is Freescale's own free graphical component. The complimentary Freescale embedded graphical user interface (eGUI) allows single chip microcontroller (MCU) systems to implement a graphical user interface and drive the latest generation of the color graphics LCD panels with the integrated display RAM and the simple serial peripheral interface (SPI) or a parallel bus interface.

#### **Communication services**

The communication interface offers services to communicate between the devices via USB 2.0 or BLE. JTAG and UART are meant for the debugging purpose. The following list presents the main features of the communication services:

- Serial interface communication via serial driver

- MQX 3.8 has USB HOST and DEVICE stack supporting LS and FS speeds.

- o LTD flash is shown as hard disk in USB communication

- HS support availability is expected e/o 2012 in MQX.

- $\circ$  OTG stack support is expected in MQX at 7/2012.

- Protocol definition between host and LTD

- BLE data transfer interface

- PXP BLE profile is supported. The Profile is done following the specification PXP\_SPEC\_V10. (6).

#### **FFS** services

The Freescale MQX File System (MFS) is an embedded FAT file system compatible with the Microsoft Windows and MS-DOS file systems. It can format, read, write and exchange files with any operating systems running a FAT-12, FAT-16 or FAT-32 files system. It is fully re-entrant and uses the Freescale MQX RTOS file device driver to access disk devices. Also, included with the Freescale MQX RTOS is a Trivial File System (TFS) that can be used in HTTP applications requiring a simple read-only file system.

MFS provides a library of functions. The functions let an embedded application access the file system in a manner that is compatible with the MS-DOS Interrupt 21 functions. All the functions guarantee the application tasks a mutually exclusive access to the file system. MFS is a device driver that an application must install over a lower-level device driver.

#### **Measurement services**

The Measurement services module is an imaginary specification for example to serve some specific measurement application. The measurement can be handled by an external I/O measurement board.

The measurement related functions could be as the following functions:

- FlexTimer controlling to give a pulse length definition via DAC

- DAC controlling for example the current or voltage output value creation

• ADC sampling would be used to get the measurement results as feedback.

#### **Debugging Facilities**

Debugging is done over the JTAG-connection. The connector includes signals for Trace capturing and programming. JTAG debugging options should be defined in the project options depending on the software work bench.

#### 4.3.3 LTD Hardware Abstraction Layer

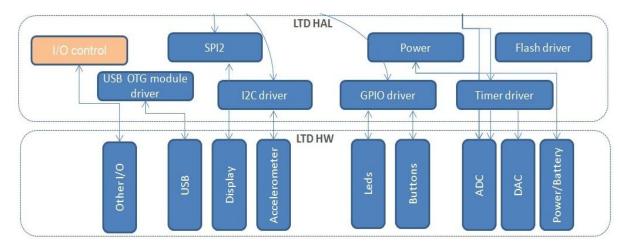

The hardware block diagram is described in the LT Engine HW Block Diagram. (7). The LTD HAL development follows based on that HW concept. See the MQX IO Drivers User Guide document for using drivers. (8). See the GPIO mapping in the document LT Engine Hardware Specification. (9, p.28-44). The LTD HAL level implements the HW adaptations as figure 7 presents.

FIGURE 7. LTD Hardware Abstraction Layer (HAL)

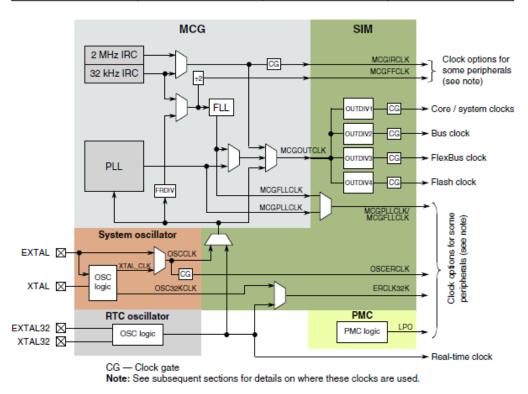

#### **Clock Generation**

Figure 8 presents the clock generation of the Kinetis K20/K60 based chips. The system starts up by using an internal 32 kHz oscillator. It is used until the external clocks are started. As a default the software configures the clock to use external crystal and enables internal Phase Lock Loop (PLL) in the Frequency Lock Loop (FFL) Bybassed External

(FBE) mode. It is important to notice that as the default Freescale K60 software uses external clock instead crystal.

The clock frequencies in the LTD are:

- System oscillator is 8MHz

- Real Time Clock (RTC) oscillator is 32kHz

The multipurpose Clock Generation (MCG) Control 1 Register (MCG\_C1) has settings for the system clock in a normal operation. The recommended operating mode is High-frequency mode 1, low power. The selection is configured in the MCG Control 2 Register (MCG\_C2). The clock rate settings are configured for MQX in the bsp\"board".h header file and other clock configurations are in the init\_hw.c file. The following configuration must be defined in the LTD\_BOARD\_twrk60n512.h header file.

|                                                                                                                                            | */<br>(8000000ul) // oscillator freq<br>(2000000ul) // must be 2-4MHz      |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| <pre>#define BSP_CORE DIV #define BSP_BUS_DIV #define BSP_FLEXBUS_DIV #define BSP_FLASH_DIV #define BSP_USB_DIV #define BSP_USB_FRAC</pre> | (1)<br>(1)<br>(2)<br>(1)                                                   |

| /* BSP_CLOCK_MUL from int<br>#define BSP_CLOCK_MUL                                                                                         | erval 24 - 55 BSP_CORE_CLOCK = 48MHz */<br>(24)                            |

| #define BSP_REF_CLOCK_DIV<br>#define BSP_CLOCK                                                                                             | (BSP_CLOCK_SRC / BSP_REF_CLOCK_SRC)<br>(BSP_REF_CLOCK_SRC * BSP_CLOCK_MUL) |

| /* CORE CLK, max 100MHz*/<br>#define BSP_CORE_CLOCK                                                                                        | (BSP_CLOCK / BSP_CORE_DIV)                                                 |

| <pre>/* SYSTEM CLK, max 100MHz #define BSP_SYSTEM_CLOCK</pre>                                                                              |                                                                            |

| /* max 50MHz */<br>#define BSP_BUS_CLOCK<br>#define BSP_FLEXBUS_CLOCK                                                                      | (BSP_CLOCK / BSP_BUS_DIV)<br>(BSP_CLOCK / BSP_FLEXBUS_DIV)                 |

| /* max 25MHz */<br>#define BSP_FLASH_CLOCK                                                                                                 | (BSP_CLOCK / BSP_FLASH_DIV)                                                |

|             | OSC    | MCG    | SIM                  |

|-------------|--------|--------|----------------------|

| Muliplexers | MCG_Cx | MCG_Cx | SIM_SOPT1, SIM_SOPT2 |

| Dividers    | -      | MCG_Cx | SIM_CLKDIVx          |

| Clock gates | OSC_CR | MCG_C1 | SIM_SCGCx            |

FIGURE 8. Clock Generation of Kinetis

#### **EEPROM**

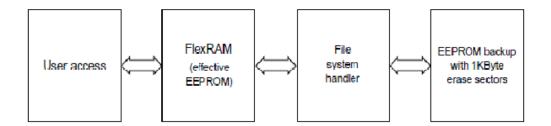

To provide an enhanced EEPROM functionality, the FlexMemory uses a RAM block (FlexRAM), a flash block (FlexNVM), and an EEE state machine. When the EEE functionality is enabled, the FlexRAM becomes the user's EEE memory. The FlexRAM address space is where one accesses all of the EEE data. The detailed description of the Kinestis EEPROM is shown in EEPROM configuration instructions document. (10.)

FIGURE 9. Eeprom solution in Kinetis (10).

# MQX I/O

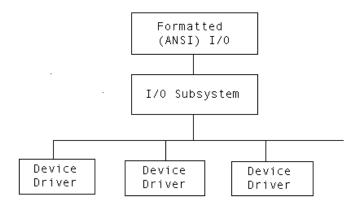

The MQX I/O subsystem implementation is a slightly deviated subset of the POSIX standard I/O. It follows the UNIX model of open, close, read, write, and ioctl functions. The I/O subsystem makes calls to I/O device-driver functions. The MQX I/O uses the pointers to the FILE, as returned by fopen(), instead of the file descriptors (FDs). The MQX I/O has three layers as presented in figure 10. (8.)

FIGURE 10. MQX I/O layers (8).

## **Device I/O Control**

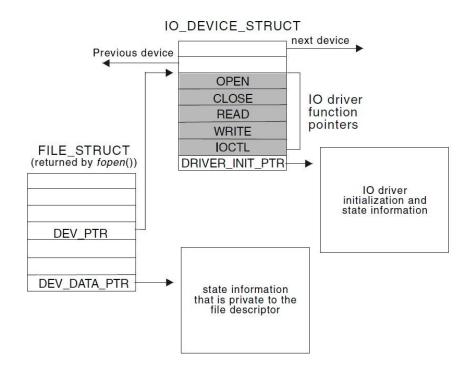

Figure 11 shows the relationship between a file handle (FILE\_STRUCT) that is returned by fopen(), the I/O device structure (allocated when the device is installed), and the I/O driver functions for all I/O device drivers. (8.)

FIGURE 11. I/O Device Structure — I/O Device Drivers (8).

# Serial I/O Control

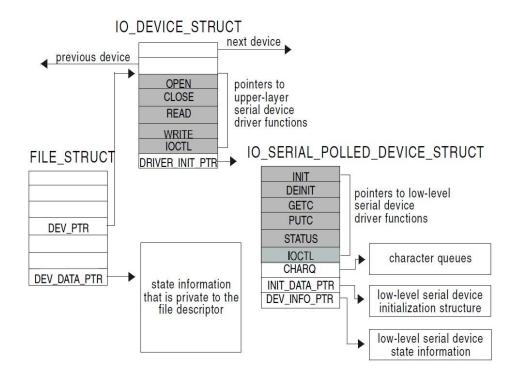

The serial device drivers are complex in that they have a generic driver layer and a lowlevel standard simple interface to the serial hardware. Figure 12 shows the relationship between a file handle (FILE\_STRUCT) that is returned by fopen(), the I/O device structure (allocated when the device is installed), and the upper-level serial-device driver functions. (8.)

FIGURE 12. I/O Device Structure — Serial-Device Drivers (8).

## **USB On The Go Driver**

The LTD engine supports the USB 2.0 interface in the LS and FS modes. The supported modes are Device, OTG. The design can also support USB Host protocol, but the power supply to VBUS is limited to the level that is required in the OTG-mode when the device is acting as host, i.e. 5V / 8mA rather than 5V / 500mA as required for the standard USB host.

In the Device mode the VBUS voltage is regulated down to the 3.3V inside processor. The data lines of the USB are terminated to that voltage with internal termination resistors.

The USB OTG implementation requires an external component MAX3353E, which supplies the power to VBUS, includes the ESD protection and a possibility to terminate the data lines. MAX3353E is controlled by I2C (I2C0).

TABLE 1. Pin description of USB cable (9).

| Pin | Signal |

|-----|--------|

| 1   | VBUS   |

| 2   | D-     |

| 3   | D+     |

| 4   | ID     |

| 5   | GND    |

# I2C Driver

The chip has three I2C channels. The desired I2C I/O control is taken into use by activating that in the user\_config.h header file. The I2C specific commands and the definition are presented in the i2c.h file. The I2C I/O driver's use example is shown below.

```

/* first, initialize the file descriptor */

MQX_FILE_PTR i2C1_fd = NULL;

/* open I2C1 channel */

i2c1_fd = fopen("i2c1:", NULL);

if (NULL == i2c1_fd)

{

printf ("Error opening I2C driver!\n");

_time_delay (200L);

_task_block ();

}

/* IOCTL calls specific to I2C */

i2c.h

```

#### **SPI Driver**

The chip has three SPI channels, SPI0, SPI1 and SPI2. The desired SPI I/O control is taken into use by activating it in the user\_config.h header file. The SPI specific commands and the definition are presented in spi.h. The SPI Driver's use example is shown below.

```

/* first, initialize the file descriptor */

MQX FILE PTR spifd = NULL;

/* open SPI2 channel */

spifd = fopen("spi2:", NULL);

if (NULL == spifd)

printf ("Error opening SPI driver!\n");

time delay (200L);

_____ueray (2

__task_block ();

/* Set device mode */

param = SPI DEVICE MASTER MODE;

if (SPI_OK == ioctl (spifd, IO_IOCTL_SPI_SET_TRANSFER_MODE, &param))

{

printf ("device mode SET OK\n");

/* write operation */

if (SPI OK == ioctl (spifd, IO IOCTL SPI READ WRITE, &rw struct))

/* printf ("line data sent OK\n"); */

}

/* IOCTL calls specific to SPI */

see spi.h

```

# **GPIO Driver**

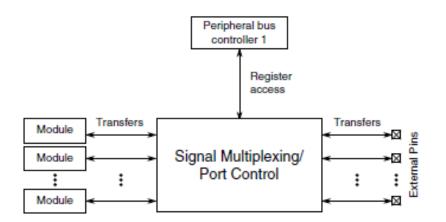

The I/O Pins of the CPU can be multiplexed to different functional modules. Each individual I/O pin has a control register to select the multiplexing and to setup the hardware configuration of the pin. The processor has five 32-pin ports as figure 13 shows. Each 32-pin port is assigned one interrupt. The digital filter option has two clock source options: bus clock and 1-kHz LPO. The 1-kHz LPO option gives the user this feature in low power modes. The digital filter is configurable from 1 to 31 clock cycles when enabled. See GPIO mapping of the LTD in the document LT Engine Hardware\_Specification. (9, p.28-44).

FIGURE 13. Signal Multiplexing and Port Control (12).

### **GPIO driver in LTD Board Support Package implementation**

Three on/off buttons are connected to the GPIO pins. The buttons can be used to simulate a simple UI or used for different control purposes depending on the application's need. One LED is reserved for each control button. If UI is not implemented, the LEDs can be used for example to indicate different operating modes. The TWR MQX GPIO driver implementation is ported to LTD\_BOARD BSP. The use of GPIO goes in the same way as the use of the other drivers. See the following GPIO driver use example.

```

/* define gpio pin */

#define LCD EXTCOMIN (GPIO PORT D | GPIO PIN5)

/\star define pin list and default values of them (pin listing is not mandatory if

just one signal is in question) */

uint_32 extcomin_pin[] =

LCD EXTCOMIN | GPIO PIN STATUS 1,

GPIO LIST END

};

/* ... in the function

first, initialize the file descriptor */

MQX FILE PTR extcomin fd = NULL;

/* Open gpio port as output ("gpio:write") */

extcomin_fd = fopen ("gpio:write", (char_ptr) & extcomin pin);

if (NULL == extcomin fd)

printf ("Error opening extcomin GPIO!\n");

__time_delay (200L);

__task_block ();

/* GPIO IOCTL commands from io_gpio.h */

```

# **Analog-to-Digital Converter Driver**

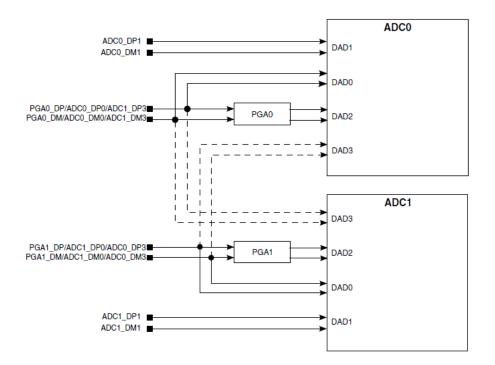

The Desired ADC I/O control is taken into use by activating that in the user\_config.h header file. The chip has two ADC channels, ADC0 and ADC1. The application specific ADC usability can be specified separately. The use of the ADC channels goes in the same way as the serial bus controlling with the open, read and write functions.

The ADC HW implementation is shown in figures 14 and 15. Figure 14 shows ADC channels with the Pin Grid Array (PGA) integration, and the Interleaved ADC channels are presented in figure 15. The detailed information of the ADC channels is described in the document LT Engine Hardware Specification. (9.)

FIGURE 14. ADC Channels with PGA Integration (12).

FIGURE 15. Interleaved ADC channels (12).

# **Digital-to-Analog Converter Driver**

There are 2 DAC outputs. The MQX has not a DAC driver implemented as POSIX API. Therefore the DAC usability has to be built with direct register configurations. The application specific DAC usability can be specified separately.

# Power Management (PM) Driver

The three primary modes of the operation are run, wait and stop. The WFI instruction invokes both wait and stop modes for the chip. The primary modes are augmented in a number of ways to provide lower power based on the application's needs. The chip level operating modes of the processor are listed in table 2.

| Chip mode                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Core mode  | Normal<br>recovery<br>method     |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|--|

| Normal run                                | Allows maximum performance of chip. Default mode out of reset; on-<br>chip voltage regulator is on.                                                                                                                                                                                                                                                                                                                                                                       | Run        | -                                |  |

| Normal Wait -<br>via WFI                  | Allows peripherals to function while the core is in sleep mode,<br>reducing power. NVIC remains sensitive to interrupts; peripherals<br>continue to be clocked.                                                                                                                                                                                                                                                                                                           | Sleep      | Interrupt                        |  |

| Normal Stop -<br>via WFI                  | Places chip in static state. Lowest power mode that retains all registers while maintaining LVD protection. NVIC is disabled; AWIC is used to wake up from interrupt; peripheral clocks are stopped.                                                                                                                                                                                                                                                                      | Sleep Deep | Interrupt                        |  |

| VLPR (Very<br>Low Power<br>Run)           | On-chip voltage regulator is in a low power mode that supplies only<br>enough power to run the chip at a reduced frequency. Reduced<br>frequency Flash access mode (1 MHz); LVD off; internal oscillator<br>provides a low power 2 MHz source for the core, the bus and the<br>peripheral clocks.                                                                                                                                                                         | Run        | Interrupt                        |  |

| VLPW (Very<br>Low Power<br>Wait) -via WFI | Same as VLPR but with the core in sleep mode to further reduce<br>power; NVIC remains sensitive to interrupts (FCLK = ON). On-chip<br>voltage regulator is in a low power mode that supplies only enough<br>power to run the chip at a reduced frequency.                                                                                                                                                                                                                 | Sleep      | Interrupt                        |  |

| VLPS (Very<br>Low Power<br>Stop)-via WFI  | Places chip in static state with LVD operation off. Lowest power mode<br>with ADC and pin interrupts functional. Peripheral clocks are stopped,<br>but LPTimer, RTC, CMP, TSI, DAC can be used. NVIC is disabled<br>(FCLK = OFF); AWIC is used to wake up from interrupt. On-chip<br>voltage regulator is in a low power mode that supplies only enough<br>power to run the chip at a reduced frequency. All SRAM is operating<br>(content retained and I/O states held). | Sleep Deep | Interrupt                        |  |

| LLS (Low<br>Leakage Stop)                 | State retention power mode. Most peripherals are in state retention<br>mode (with clocks stopped), but LLWU, LPTimer, RTC, CMP, TSI,<br>DAC can be used. NVIC is disabled; LLWU is used to wake up.<br>NOTE: The LLWU interrupt must not be masked by the interrupt<br>controller to avoid a scenario where the system does not fully<br>exit stop mode on an LLS recovery.                                                                                               | Sleep Deep | Wakeup<br>Interrupt <sup>1</sup> |  |

|                                           | All SRAM is operating (content retained and I/O states held).                                                                                                                                                                                                                                                                                                                                                                                                             |            |                                  |  |

| VLLS3 (Very<br>Low Leakage<br>Stop3)      | Most peripherals are disabled (with clocks stopped), but LLWU,<br>LPTimer, RTC, CMP, TSI, DAC can be used. NVIC is disabled; LLWU<br>is used to wake up.                                                                                                                                                                                                                                                                                                                  | Sleep Deep | Wakeup Reset <sup>2</sup>        |  |

|                                           | SRAM_U and SRAM_L remain powered on (content retained and I/O states held).                                                                                                                                                                                                                                                                                                                                                                                               |            |                                  |  |

| VLLS2 (Very<br>Low Leakage<br>Stop2)      | Most peripherals are disabled (with clocks stopped), but LLWU,<br>LPTimer, RTC, CMP, TSI, DAC can be used. NVIC is disabled; LLWU<br>is used to wake up.                                                                                                                                                                                                                                                                                                                  | Sleep Deep | Wakeup Reset <sup>2</sup>        |  |

|                                           | SRAM_L is powered off. A portion of SRAM_U remains powered on (content retained and I/O states held).                                                                                                                                                                                                                                                                                                                                                                     |            |                                  |  |

| VLLS1 (Very<br>Low Leakage<br>Stop1) | Most peripherals are disabled (with clocks stopped), but LLWU,<br>LPTimer, RTC, CMP, TSI, DAC can be used. NVIC is disabled; LLWU<br>is used to wake up. | Sleep Deep | Wakeup Reset <sup>2</sup> |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|

|                                      | All of SRAM_U and SRAM_L are powered off. The 32-byte system register file and the 32-byte VBAT register file remain powered for customer-critical data. |            |                           |

| BAT (backup<br>battery only)         | The chip is powered down except for the VBAT supply. The RTC and the 32-byte VBAT register file for customer-critical data remain powered.               | Off        | Power-up<br>Sequence      |

1. Resumes normal run mode operation by executing the LLWU interrupt service routine.

2. Follows the reset flow with the LLWU interrupt flag set for the NVIC.

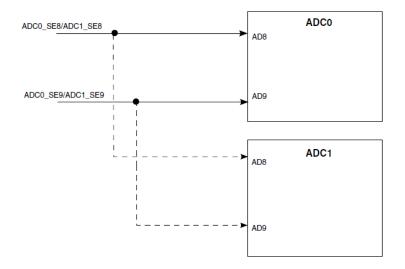

Figure 16 shows the operation mode transitions. As figure 16 presents, the operation mode transition is possible between low power modes. There can be applications which need the low power modes all the time.

- For example, in the VLPS mode some blocks (ADC, DAC etc.) and memories are powered.

- The VLPS power consumption of the microcontroller is about 50uA as mentioned in the K20 Sub-Family Datasheet. (12).

FIGURE 16. Operation mode transitions (12).

See the following example of the VLPS mode entry routine. It puts the processor into the VLPS mode directly from the normal run mode.

If the VLPS mode is entered directly from a normal RUN mode, then the LPWUI bit is forced to 1 by the hardware. This means that when an interrupt occurs the user will exit to normal run mode instead of VLPR. If, however, the VLPS mode is entered from VLPR, the state of the LPWUI bit determines the state the MCU returns to upon the exit from VLPS. If LPWUI is set and an interrupt occurs, one exits to the normal run mode instead of VLPR. If LPWUI is clear and an interrupt occurs, one exits to VLPR.

```

void enter vlps(char lpwui value)

{

/* Write to PMPROT to allow VLPS power modes write one if not all set make

sure all enabled this write-once bit allows the MCU to enter the very low

power modes: VLPR, VLPW, and VLPS. */

MC PMPROT = MC PMPROT AVLP MASK;

/* Set the LPLLSM field to 0b010 for VLPS mode - Need to set state of LPWUI

bit 8 */

if(lpwui_value)

{

MC_PMCTRL = ( MC_PMCTRL_LPWUI_MASK | // set LPWUI

MC_PMCTRL_LPILSM(2)); // set LPLLSM = 0b10

}

else

MC_PMCTRL = (!MC_PMCTRL_LPWUI_MASK | // set LPWUI

MC_PMCTRL_LPLLSM(2)); // set LPLLSM = 0b10

MC PMCTRL LPLLSM(2));

}

sleep ltd disable ports partial();

OSC CR = 0;

/* Now execute the stop instruction to go into VLPS */

/* Set the SLEEPDEEP bit to enable deep sleep mode (STOP) */

SCB SCR |= SCB SCR SLEEPDEEP MASK;

/* WFI instruction will start entry into STOP mode */

asm("WFI");

}

```

#### **Timer Driver**

See the following use example of the low power timer 0. The interrupt is generated when the compare value is reached.

```

void lptmr0_interrupt(int compare_value)

{

// disable LPT INT

_cortex_int_init(INT_LPTimer, LPT_INT_PRIORITY, FALSE);

// Clear global variable

LPTMR INTERRUPT = 0;

// Reset LPTMR module

lptmr0_clear_registers();

// install lptmr interrupt service routine

_int_install_isr(INT_LPTimer, lptmr0_isr, NULL);

// Enable LPTMR0 Interrupt in NVIC

_cortex_int_init(INT_LPTimer, LPT INT PRIORITY, TRUE);

// Set compare value

LPTMR0 CMR = LPTMR CMR COMPARE (compare value);

// Use LPO clock and bypass prescale

LPTMR0 PSR = LPTMR PSR PCS(0x1) | LPTMR PSR PBYP MASK;

// Enable LPT interrupt

```

```

LPTMR0_CSR = LPTMR_CSR_TIE_MASK;

// Turn on LPTMR and start counting

LPTMR0_CSR |= LPTMR_CSR_TEN_MASK;

// Wait for the global variable to be set in LPTMR ISR

while(LPTMR_INTERRUPT == 0) {}

DEBUG_PRINT1("Timer should have waited for %d msec\n", compare_value);

// Turn off LPT to avoid more interrupts

LPTMR0_CSR &= ~LPTMR_CSR_TEN_MASK;

// Reset LPTMR module

lptmr0_clear_registers();

```

### **Flash RW Driver**

}

The Freescale MQX File System (MFS), which is used on the flash memory driver, is an embedded FAT file system compatible with Microsoft Windows and with the MS-DOS file systems. It can format, read, write and exchange files with any operating systems running a FAT-12, FAT-16 or FAT-32 files system. Examples of the lower-level drivers are drivers for memory devices, flash disks, floppy disks, or partition-manager devices. MFS uses the lower-level driver to access the hardware device.

The creation of the file system is possible when the chip packet has Flex NVM memory. See more information about the Flex memory and EEPROM configuring in document EEPROM configuration instructions. (10).

### **Display Driver**

The Sharp 96 \* 96 pixel 1.35 inch display is used. The Screen refresh is done by its own display task. ShowFrame() function is a interface for higher application layers. The Sharp LCD is controlled by the SPI controller. The SPI controller has to be configured in the way that the LTD is a master. The data is transferred Least Significant Bit (LSB) first. The chip select must stay high during the burst (one line or frame). The frame size has to be set accordingly or the end of the queue flag has to be used and a continuous chip select has to be enabled. Display must be refreshed within a certain interval. The refreshing is done using the EXTCOMIN pin of the display interface. The EXTCOMIN signal is connected to PTE26. The output can be either software controlled or a 1Hz clock output from RTC. The

DISP signal is used to switch on the display ON or OFF. It is connected to PTD15 and it is Software controlled output. The display signal interface is shown in table 3.

| TERMINAL | SYMBOL   | I/O   | FUNCTION                                        | NOTES |

|----------|----------|-------|-------------------------------------------------|-------|

| 1        | SCLK     | INPUT | Serial clock signal                             |       |

| 2        | SI       | INPUT | Serial data input signal                        |       |

| 3        | SCS      | INPUT | Chip select signal                              |       |

| 4        | EXTCOMIN | INPUT | External COM inversion signal input (H: enable) | 1     |

| 5        | DISP     | INPUT | Display ON/OFF signal                           | 2     |

| 6        | VDDA     | POWER | Power supply (Analog)                           |       |

| 7        | VDD      | POWER | Power supply (Digital)                          |       |